Gatekeeper

(Courtesy of SA BEST)

Teams are tasked with building central processing units (CPUs) by collecting and converting components in three fabrication processes:

- Collecting and placing transistor containers to create electronic gate (AND, OR, NOT, NAND) circuits.

- Placing gate circuits in the correct combination into production to create integrated circuits (multiplexer, adder, decoder, data-latch).

- Placing the correct integrated circuits (ICs) into a template to create a CPU.

The electronic components are represented by various game pieces: Dowel rods represent transistor containers, hangers of different colors represent the gate circuits, and foam-board shapes represent the integrated circuits. Each of the fabrication processes is located in a distinct area of the game field. As components are fabricated, they are tracked (virtually) in software and are available as soon as they are fabricated and until they are consumed in creating a higher-level component. Although each team has its own virtual inventory, the field is always reset to the same configuration at the start of each match. There are no penalties for placing components that are not in a team’s inventory.

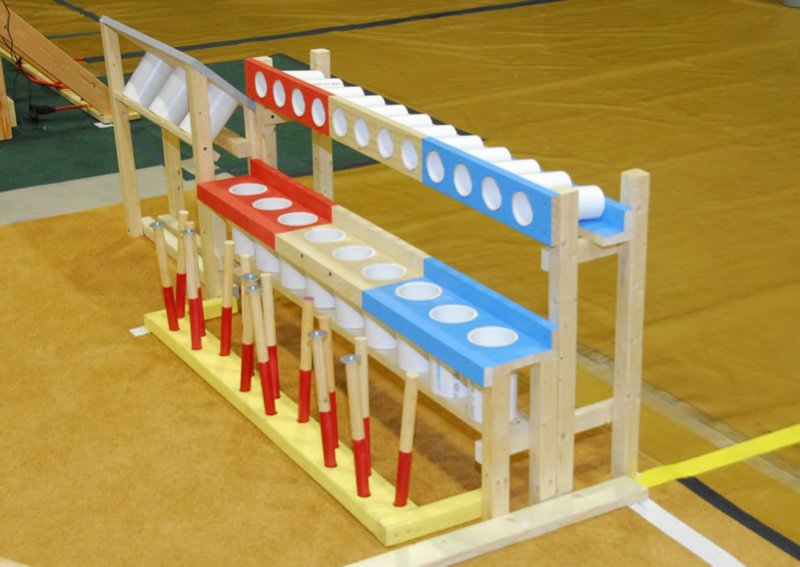

View of blue quadrant of the field with the gate fabrication area to the right and the IC fabrication area to the left.

In the gate fabrication area, the robot can place the transistor containers (dowels) into different receptacles to produce the gates indicated. Although each container holds 96 transistors, the number that can be used to produce gates depends on which end of the dowel is placed into the receptacle, and whether the upper or lower receptacle is used. The table below provides the number of transistors used based on the placement. To produce an AND, OR, or NOT gate, 24 transistors are required. A NAND gate requires 16 transistors. The dowels have to stay in the receptacle on their own to count as being properly placed.

Gate |

Transistors Required |

Transistors Collected |

Transistors Collected |

AND (blue) |

24 |

paint out: 96 |

paint up: 48 |

OR (white) |

24 |

paint out: 96 |

paint up: 48 |

NOT (red) |

24 |

paint out: 96 |

paint up: 48 |

NAND (black) |

16 |

N/A |

paint up: 94 |

Gate fabrication area with transistor containers standing upright. Each color receptacle produces a different type of gate.

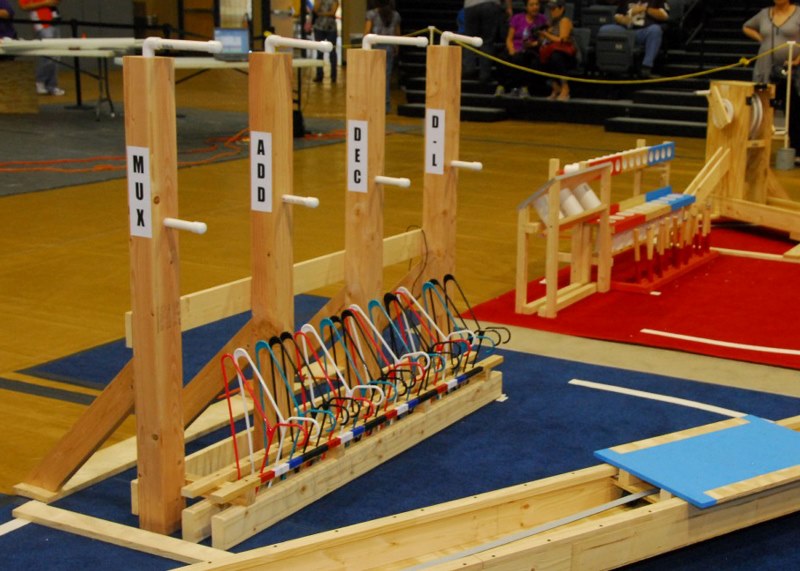

In the IC fabrication area, ICs are produced by placing gates (hangers) onto pegs on one or more of the IC towers. Each IC tower produces a different circuit as indicated in the figure and each circuit has two different gate combinations that can be used to produce the IC: one of the combinations uses only NAND gates, while the other requires a specific number of AND, OR and NOT gates as indicated in the table that follows. Depending on whether the gates are placed onto the upper or lower peg on a tower, the number of ICs produced can be either one (lower peg) or two (upper peg) per gate combination. However, gates placed on the upper peg also require double the number of gates in inventory to support the IC production; that is, the upper peg consumes gate inventory at twice the amount as the lower peg. If any gates are placed on the lower pegs of a tower, that tower will only produce at a single IC per gate combination rate. The hangers must hang directly from a peg, and not from other hangers, to be considered properly placed.

Circuit |

AND |

OR |

NOT |

or | NAND |

| MUX | 2 | 1 | 1 | 3 | |

| ADDER | 1 | 1 | 1 | 2 | |

| DECODER | 1 | 1 | 0 | 2 | |

| D-LATCH | 1 | 1 | 1 | 1 |

IC fabrication area with hangers representing gates below and vertical IC fabrication towers.

The CPU fabrication area consists of two templates into which ICs (foam-board cut-outs) can be placed to create a core processor and a memory module. As shown in the figure, the core processor requires three registers, one instruction decoder and a complete arithmetic logic unit (ALU) consisting of an adder and a multiplexer (MUX). Two different types of CPUs can be completed based on the completion of the memory module: an 8-bit CPU requires a single data-latch, while a 32-bit CPU requires four data-latches and an address decoder. The core processor can be completed over multiple matches; however, the memory module must be completed within a single match. To be considered properly placed, the ICs must be located in the appropriate receptacle in the template and placed such that they are completely flat against the lower surface of the CPU fabrication assembly.

CPU fabrication area with the ICs in the rack below that must be placed into the template above. On the template, the right side is the memory area and the left side is the core processor that requires a MUX, ADDER, DECODER and 3 D-LATCHES.

The point values that are assigned to components as they are fabricated are:

| Circuit | Value |

| AND/OR/NOT Gate | 10 points |

| NAND Gate | 8 points |

| MUX IC |

80 points |

| Adder IC | 60 points |

| Decoder IC | 40 points |

| Data-Latch IC | 60 points |

| Register | 90 points |

| Instruction Decoder | 60 points |

| MUX in ALU | 120 points |

| Adder in ALU | 90 points |

| 8-bit Memory Module | 90 points |

| 32-bit Memory Module | 420 points |

| 8-bit CPU Complete | 512 points |

| 32-bit CPU Complete | 1024 points |

In addition to points earned by fabricating components, teams may earn a bonus based on the number of matches they complete where no game pieces have been removed from play, or left on the floor and not in contact with the robot. The bonus is computed at the end of each match and may change over time as the number of matches in which a team earns the bonus changes. The bonus amount, which is applied only once and not final until the last match in the competition phase has been completed, is computed as:

Bonus = (Bonus Matches)/(Total Matches)*10%*Cumulative Score

Separate bonus scores are computed for each competition phase (i.e., seeding, semi-finals, and finals).

There are numerous restrictions on how the game is played. A partial list of some of the basic restrictions is provided here:

- Robots must remain mounted to the trolley platform for the entire match.

- Four 2-inch wide binder clips are part of the trolley and must be used for clamping the robot to the platform.

- A game piece must be in the proper position at the end of the match and must not be in contact with the robot in order to count as being properly placed for scoring/inventory purposes.

- No robot part or game pieces may be dropped within the trolley assembly. A 20-second penalty will be assessed for such an infraction.

- Items should not be dropped within the safety arc. Should this occur, the team may not run over the part, but the robot can remove the part or the team can take a 20-second penalty to allow a referee to remove the part.

- The spotter may only manipulate the trolley assembly using the cranks.

- Game pieces may be recovered from the floor by the robot, but pieces that fall outside of the quadrant are out of play.

There are three phases to the contest: a partial round robin seeding competition, a six game round robin semi-final between the top eight teams, and a three game round robin final between the top four teams. During the seeding competition, each team plays the same number of games against randomly selected opponents. The team’s total score during the seeding competition is used to rank the team and to determine seven of the eight teams that advance to the semi-final round robin playoff.

The eighth team for the semi-finals is the winner of a single “wildcard” game. The participants for the wildcard game are selected based on the score of their engineering notebook which all teams are required to submit. During the wildcard game, there are no inventory restrictions, so teams can fabricate any components without regard to what components they have in inventory.

At the start of the semi-finals, the scores are reset to zero, and teams are provided with an initial inventory of three AND, three OR, and three NOT gates and one MUX, two d-latches, and one decoder IC. For the semi-final round robin playoff, the top eight teams each play three matches. The total of each team’s scores for these three matches determines which four teams advance to the finals. For the final competition, total scores are again reset to zero and the same initial inventory provided for the semi-final matches is provided. The top four teams play three additional matches to determine the final ranking order.

Announcements

Announcements